# EMC COMPO 2024

October 7<sup>th</sup>-9<sup>th</sup>, 2024 Politecnico di Torino Torino, Italy

The 14<sup>th</sup> International Workshop on the Electromagnetic Compatibility of Integrated Circuits

> Advanced Program

As of September 26, 2024

Advancing Technology

for Humanity

# Politecnico di Torino

Department of Electronics and Telecommunications

# CONTENTS

| Welcome message             | 2  |

|-----------------------------|----|

| Sponsors                    | 3  |

| The venue                   |    |

| Committees                  | 11 |

| The exhibition              | 12 |

| Program at a glance         | 13 |

| Invited talks               |    |

| Tutorials                   | 17 |

| Networking Events           | 19 |

| Technical sessions          | 20 |

| Poster Sessions             | 37 |

| Acknowledgment of reviewers | 40 |

The 14th International Workshop on the Electromagnetic ComPO 2024 October 7<sup>th</sup>-9<sup>th</sup>, 2024 Compatibility of Integrated Circuits (Torino, Italy

# WELCOME MESSAGE

#### Dear Attendees,

I am delighted and privileged to welcome you to the 14<sup>th</sup> International Conference on the Electromagnetic Compatibility of Integrated Circuits, that will take place in Torino from October 7<sup>th</sup> to 9<sup>th</sup>. The event is held and organized by Politecnico di Torino, with the technical sponsorship of the IEEE EMC Society and the patronage of the Province of Torino.

This is the second time we have organized the workshop in Torino, the first was in 2007. That edition was a great success, but according to the technical program, this year's edition promises to be even better.

With over sixty submitted regular papers coming from sixteen different countries, accepted papers have been arranged into eight oral and three poster sessions. Three keynote speeches will be given during the Workshop: Prof. Makoto Nagata from Kobe University, Japan, Dr. Subrahmanyam Boyapati from Synopsis, Ireland and Prof. Jun Imaoka from Nagoya University, Japan. Moreover, we will have two interesting tutorials taking place on October 7<sup>th</sup> and 8<sup>th</sup>.

Furthermore, I welcome you to Torino, Roman castrum, medieval town, first capital of Italy. Torino offers a lasting memory of castles, old beautiful palaces, royal residences and monuments. Torino is one of the cultural leading cities in Italy. The city's lively cultural scene includes music, theatre, visual arts, photography, film, design, dance and heritage as well as a wide choice of museums. For many centuries, it has evolved from an ancient city into a flagship of modern technology, excelling in the fields of Automotive, Aerospace and Electronics.

As the General Chair of this workshop, I would like to thank all the members of the Local Organizing Committee (LOC) and all those who have worked tirelessly to make EMC COMPO 24 possible. Finally, I would like to thank all the authors, chairmen, reviewers, sponsors, exhibitors and attendees.

Please, enjoy the workshop, meet your colleagues and friends, ask the experts, and make the event a real success. My colleagues and I will be pleased to meet and warmly welcome you.

Prof. Franco Fiori General Chair of EMC COMPO 2024

SPONSORS

## **GOLD SPONSORS**

Competenza ed entusiasmo per soluzioni tecniche

### SILVER SPONSORS

ROHDE & SCHWARZ Make ideas real

# **CO-TECHNICAL SPONSORS**

# **ORGANIZED BY**

# Politecnico di Torino

Department of Electronics and Telecommunications

# THE VENUE

The 14<sup>th</sup> International Workshop on the Electromagnetic Compatibility of Integrated Circuits will be held at

**Politecnico di Torino Lingotto** Via Nizza 230 10126, Torino (TO), Italy

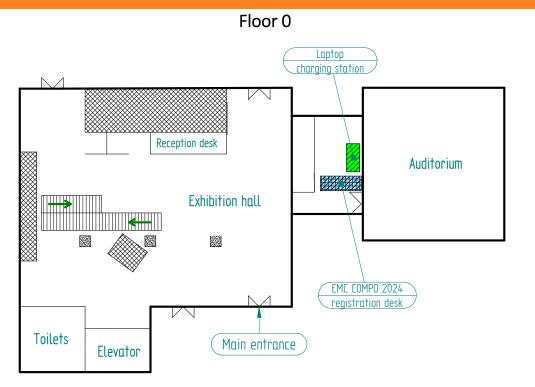

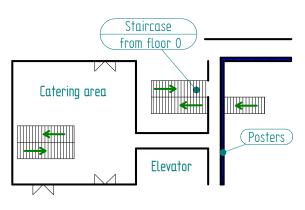

### VENUE MAP

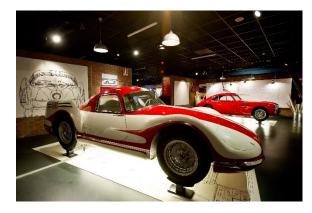

### TORINO LINGOTTO: A HISTORICAL AND ARCHITECTURAL ICON

**History**: Torino Lingotto, located in Turin, Italy, was originally a car factory built by FIAT. Construction began in 1916, and the factory was inaugurated in 1923. Designed by architect Giacomo Matté-Trucco, the building was revolutionary for its time, featuring a unique five-floor structure where raw materials entered at the ground level and finished cars emerged at the rooftop level, ready to be tested on the 1.5 km long rooftop track. This innovative design was highly praised by renowned architect Le Corbusier.

**Importance**: The Lingotto factory was one of the largest and most advanced car factories in the world when it opened. It played a crucial role in the industrialization of Turin and significantly influenced modern industrial architecture. The factory produced around 80 different car models, including the famous FIAT Topolino. However, by the late 1970s, the factory became obsolete and was closed in 1982.

Transformation: In the late 1980s, the Lingotto complex underwent a major transformation led by

architect Renzo Piano. It was converted into a multi-purpose center that now includes concert halls, a theatre, a convention center, shopping arcades, and a hotel. The rooftop test track was preserved and remains a notable feature of the building.

Today, Lingotto stands as a symbol of Turin's industrial heritage and its ability to adapt and innovate. It continues to be a significant cultural and commercial hub in the city.

### HOW TO GET TO THE VENUE

#### FROM TORINO CASELLE AIRPORT

You can reach the Workshop Venue (Politecnico Lingotto) from the Caselle airport either using public transport or by car.

#### BY CAR

After arriving at the airport in Caselle Torinese, you will reach the Workshop venue (Politecnico di Torino Lingotto located at Via Nizza, 230, 10126 Torino) in about 50 minutes by car. Start by heading towards Via Torino/SP2, which is just 1.4 km from the airport and takes around 3 minutes. From there, follow the Raccordo Autostradale Torino - Caselle/RA10, driving in the direction of Torino city center for about 10 minutes (11.7 km). Continue on Via Chiesa della Salute, then take Corso Principe Oddone, and proceed along C.so Vittorio Emanuele II, C.so Galileo Ferraris, and Corso Bramante for around 23 minutes (8 km). Finally, follow Via Nizza and you will reach your destination in approximately 3 minutes (350 m).

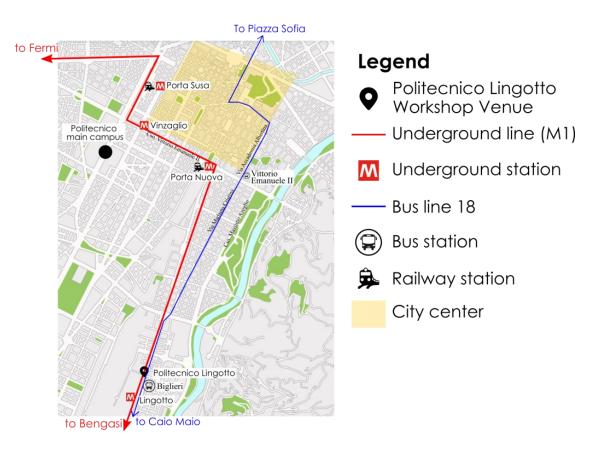

#### TRAIN + UNDERGROUND

- Duration: approximately 1 hour and 10 minutes, with one train every 30 minutes.

- Cost: € 5.70 (€ 3.70 for the train ticket, € 2 for the underground)

From Torino Airport's Caselle railway station, take a train to the city center. The station is located opposite the Arrivals area of the terminal. The final destination of the train will be either Fossano or Alba (SFM lines 4 or 7). Get off at Porta Susa station and transfer to the metro. The nearest underground stations are "Porta Susa" or

"XVIII Dicembre." Take the metro towards Bengasi and get off at the "Lingotto" station. The venue is a 5minute walk from there.

#### ARRIVA BUS + UNDERGROUND

- Duration: approximately 1 hour, with one bus every 15/30 minutes.

- Cost: € 9.50 (€ 7.50 for the bus ticket, € 2 for the underground)

From Torino Airport Caselle, take the Arriva bus to the city center (either the 9-stop or 3-stop express route). The bus will drop you at Piazza Carlo Felice, directly in front of Porta Nuova railway station. From "Porta Nuova," take the metro towards Bengasi and get off at the "Lingotto" station. The venue is a 5-minute walk from there.

#### FROM CITY CENTER

The Workshop Venue is well connected to Torino's city center via the M1 metro line, with trains running every 3 to 5 minutes. From the Politecnico di Torino main campus (Corso Duca degli Abruzzi 24), the closest metro station is "Vinzaglio," located between Porta Susa and Porta Nuova. The nearest metro station to the venue is "Lingotto," next to the Lingotto mall. Alternatively, you can reach the venue by bus (line 18).

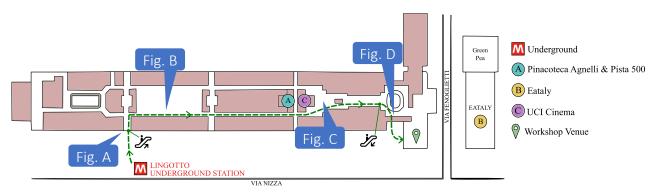

#### ROUTE TO THE VENUE THROUGH EIGHT GALLERY

Below, you will find detailed instructions on how to reach the Venue from the "Lingotto" underground station via the Eight Gallery mall:

- 1. Exit "Lingotto" station through the **right** exit marked "Centro Polifunzionale Lingotto.

- 2. Head straight to the entrance in front of you, near "Torino Lingotto Centro Congressi."

- 3. Go up to the first floor, then turn **right**.

- 4. Walk straight along the corridor.

- 5. After Feltrinelli bookshop, take the stairs down to the ground floor.

- 6. Exit near Portello Caffè.

- 7. The Workshop venue will be on your left.

Figure A - Eight Gallery entrance.

Figure C - Inside the Eight Gallery.

Figure B - Inside the Eight Gallery.

Figure D - Exit.

### NEARBY ATTRACTIONS

#### Museo Nazionale dell'Automobile

Located just a short walk from Lingotto, this museum showcases the history of the automobile with a vast collection of cars and interactive exhibits.

<u>Address</u> Corso Unità d'Italia 40, 10126 Torino

<u>Website</u> https://www.museoauto.com/en/

Opening hours (Ticket office always closes one hour earlier)MONDAYfrom 10:00 AM to 02:00 PMTUESDAY to SUNDAYfrom 10:00 AM to 07:00 PM

#### Pinacoteca Giovanni e Marella Agnelli

Situated within the Lingotto complex, this art gallery features a collection of masterpieces from renowned artists such as Matisse, Canaletto, and Picasso. La Pista 500: The rooftop test track of the former Fiat factory, now a unique space for events and exhibitions.

#### <u>Address</u>

Via Nizza, 230/103, 10126 Torino

Opening hours (Last entrance 30 mins before closing)MONDAYclosedTUESDAY to SUNDAYfrom 11:00 AM to 07:00 PM

Pinacoteca Agnelli and Pista 500 can be reached by entering the Lingotto center from <u>via Nizza 262</u> (Metro Lingotto) or <u>via Fenoglietti 15</u> (in front of Eataly) and following the signs inside the shopping center.

### Eataly Lingotto

A paradise for food lovers, Eataly offers a wide range of Italian food products, restaurants, and cooking classes. It's a great place to experience the culinary delights of Italy.

#### <u>Address</u> Via Ermanno Fenoglietti, 14, 10126 Torino

<u>Opening hours</u> Every day from 08:00 AM to 11:00 PM

### Parco del Valentino

A beautiful park along the Po River, perfect for a relaxing stroll. It also houses the Borgo Medievale, a replica medieval village.

#### <u>Website</u>

http://www.comune.torino.it/verdepubblico/parco-del-valentino/ https://www.turismotorino.org/it/esperienze/trekking-eoutdoor/parco-del-valentino

### Centro Commerciale Lingotto

This shopping center offers a variety of shops, restaurants, and entertainment options, making it a convenient spot for some leisure time.

<u>Address</u> Via Ermanno Fenoglietti, 15, 10126 Torino

Opening hoursShopsevery day from 10:00 AM to 08:30 PMBars and restaurantsevery day until 11:00 PM

<u>Website</u> https://www.centrocommercialelingotto.it

# COMMITTEES

# Local Organizing Committee

**General Chair** Franco Fiori – Politecnico di Torino

**TPC Chair** Flavia Grassi – Politecnico di Milano

#### Members

Francesco De Paulis - Università dell'Aquila Markeljan Fishta – Politecnico di Torino Davide Pandini – ST Microelectronics Erica Raviola – Politecnico di Torino Anna Richelli – Università degli Studi di Brescia Xinglong Wu – Politecnico di Milano

### **Technical Program Committee**

Adil El Abazzi, Thales Bordeaux, France Adrijan Barić, University of Zagreb, Croatia Alexandre Boyer, LAAS-CNRS, France Andre Durier, Continental, France Bart Boesman, Melexis, Belgium Bernd Deutschmann, TU Graz, Austria Bertrand Vrignon, NXP, France Binhong Li, IMECAS, China Bob Scully, NASA Johnson Space Center, USA Davide Pandini, ST Microelectronics, Italy Davy Pissoort, KU Leuven Bruges, Belgium Erica Raviola, Politecnico di Torino, Italy ErPing Li, Zhejiang University, China Etienne Sicard, INSA Toulouse, France Fabian Vargas, PUCRS, Brazil Franco Fiori, Politecnico di Torino, Italy Frank Klotz, Infineon, Germany Frederic Lafon, Valeo, France HarkByeong Park, Samsung, South Korea Hugo Pues, Melexis, Belgium Hyun Ho Park, Univ. of Suwon, South Korea Jack Kruppa, Infineon, Germany Jan Niehof, NXP, Netherlands

Jean-Michel Redoute, Univ. of Liege, Belgium Jeremy Raoult, Montpellier University, France Jianfei Wu, NUDT, China Kieran O' Leary, Mixed Signal Systems, UK Kamel Abouda, NXP, France Makoto Nagata, Kobe University, Japan Mart Coenen, EMCMCC, Netherlands Masahiro Yamaguchi, Tohoku University, Japan Mauro Merlo, ST Microelectronics, Italy Mohamed Ramdani, ESEO Angers, France Mototsugu Okushima, Renesas, Japan Osami Wada, Kyoto University, Japan Ramiro Serra, TU Eindhoven, Netherlands Richard Xian-Ke Gao, A\*STAR, Singapore Renaud Gillon, SYDELITY, Belgium Richard Perdriau, ESEO Angers, France Seungyoung Ahn, KAIST, Korea Sergey Miropolsky, Infineon, Germany Shih-yi Yuan, Feng Chia University, Taiwan Sonia Ben Dhia, LAAS-CNRS, France Umberto Paoletti, Hitachi Ltd., Japan Wolfgang Wilkening, Bosch, Germany

# THE EXHIBITION

A 3-days technical exhibition will be hosted to accompany the EMC Compo 2024 workshop. This is a unique opportunity for manufacturers and dealers to showcase products and services, increase visibility, and develop relationships with experts in the area of electromagnetic compatibility of integrated circuits. The exhibitions will showcase, but it is not limited to, EMC-related equipment and tools, measurement and test equipment, spectrum monitoring and measurement systems, protecting device and components, microwave instrumentation, electromagnetic analysis and synthesis software.

# PROGRAM AT A GLANCE

| From           | n-To           | Monday, 7 Oc                  | ctober     | Tuesday, 8 October                              |             | Wednesday, 9 October      |  |

|----------------|----------------|-------------------------------|------------|-------------------------------------------------|-------------|---------------------------|--|

| 8:40           | 9:00           |                               |            |                                                 |             |                           |  |

| 9:00           | 9:10           | Welcome cere                  | emony      | Invited talk #2: On Amor                        |             | Invited talk #3: CM       |  |

|                |                | Invited talk #1: Chip-        |            | Invited talk #2: OpAmps<br>highly immune to EMI |             | noise reduction in DC-    |  |

| 9:10           | 9:40           | Backside Vulner               | ability to |                                                 |             | DC converters             |  |

|                |                | IEMI in IC                    | Ès 🛛       |                                                 |             |                           |  |

| 9:40           | 10:10          | Coffee break an               | d Posters  | Coffee break and                                |             | Coffee break and          |  |

| 10.10          | 10:30          |                               |            | Posters                                         |             | Posters                   |  |

| 10:10<br>10:30 | 10:50          | -                             |            |                                                 |             |                           |  |

| 10:50          | 11:10          | TS#1: Susceptibil             |            | TS#4: EMC-c                                     |             | TS#6: Power Electronics   |  |

| 11:10          | 11:30          | of analog and                 |            | Design of ICs and<br>Guidelines                 |             | EMC                       |  |

| 11:30          | 11:50          | signals IC                    | Cs .       |                                                 |             |                           |  |

| 11:50          | 12:10          |                               |            |                                                 |             |                           |  |

| 12:10          | 12:30          |                               |            |                                                 |             |                           |  |

|                |                |                               |            |                                                 |             | Lunch break               |  |

| 12:30          | 13:00          | Lunch break                   | Tutorial   | Lunch break                                     | Tutorial    | and Posters               |  |

| 13:00          | 13:40          | and Posters                   | #1         | and Posters                                     | #2          |                           |  |

| 13:40          | 14:00          |                               |            |                                                 |             |                           |  |

| 14:00          | 14:20          |                               |            |                                                 |             |                           |  |

| 14:20          | 14:40          | TS #2: Measurement<br>methods |            | TS #5: Suscept                                  | tibility of | TS #7: SI and PI at IC    |  |

| 14:40          | 15:00          |                               |            | ICs to Intentio                                 |             | and PCB level             |  |

| 15:00<br>15:20 | 15:20<br>15:40 | for chip level                | EMC        | and ESD                                         |             |                           |  |

| 15:40          | 16:00          | -                             |            |                                                 |             |                           |  |

|                |                |                               |            |                                                 |             | Coffee break and          |  |

| 16:00          | 16:20          | Coffee break an               | id Posters |                                                 |             | Posters                   |  |

| 16:20          | 16:40          |                               |            |                                                 |             |                           |  |

| 16:40          | 17:00          |                               |            |                                                 |             | TS #8: Security and       |  |

| 17:00          | 17:20          | TS #3: Modeling f             |            |                                                 |             | Reliability issues of ICs |  |

| 17:20          | 17:40          |                               |            | Social tour                                     |             |                           |  |

| 17:40          | 18:00          |                               |            |                                                 |             |                           |  |

| 18:00          | 18:20          |                               |            |                                                 |             |                           |  |

| 18:00          | 19:30          |                               |            |                                                 |             |                           |  |

| 19:30          | 21:30          |                               |            | Gala dinner                                     |             |                           |  |

The registration desk opens on Monday 7 at 8:15.

The 14th International Workshop (EMC COMPO 2024 on the Electromagnetic Compatibility of Integrated Circuits (Torino, Italy

# INVITED TALKS

# #1: CHIP-BACKSIDE VULNERABILITY TO INTENTIONAL ELECTROMAGNETIC INTERFERENCE IN INTEGRATED CIRCUITS

PRESENTER

**PROF. MAKOTO NAGATA** KOBE UNIVERSITY, JAPAN MONDAY, 7 OCTOBER 9:10-9:40

#### ABSTRACT

The backside of integrated circuits (ICs) in flip-chip assembly is susceptible to

intentional electromagnetic interference due to its open surface. In this article, we propose a model in which conducted current noise from a localized area of the Si substrate on the chip-backside causes errors in complementary metal-oxidesemiconductor (CMOS) digital circuits. This model explains for the first time the mechanism of bit-flip errors in bistable circuits caused by high-voltage pulse (HVP) injection on the backside of the IC. The injected current from the backside of the IC not only flows into the power distribution network, but also charges the gate capacitance of the next stage via p–n junction diodes of body/drain or body/source in N-channel MOSFETs (NMOS) with twin-well structures, resulting in bit-flip errors. In this study, circuit simulations were performed using a three-dimensional RC network model of the IC chip and an HVP injector. These simulations have shown that the P-well voltage is biased depending on the arrangement of the tap cells, reproducing bit-flip errors in the bistable circuit of a D flip-flop. The simulation results were validated on a fabricated prototype IC chip, which confirmed the trend of data dependency for errors related to the physical layout.

#### PRESENTER'S BIOGRAPHY

Makoto Nagata received the B.S. and M.S. degrees in physics from Gakushuin University, Tokyo, in 1991 and 1993, respectively, and a Ph.D. in electronics engineering from Hiroshima University, Hiroshima, in 2001. He is currently a full professor with the graduate school of science, technology and innovation, Kobe University, Kobe, Japan.

He chaired the technology directions subcommittee for ISSCC (2018-2022) and now serves as its executive committee member. He was the technical program chair (2010–2011), the symposium chair (2012–2013), and an executive committee member (2014–2015) for the symposium on VLSI circuits. He was the IEEE Solid-State Circuits Society (SSCS) AdCom member (2020-2022), the distinguished lecturer (2020-2021 and 2024-present) and the chapters vice chair (2022-present) of the society.

# #2: MODELING AND DESIGN OF HIGHLY EMI IMMUNE CMOS OPAMP TOPOLOGIES

PRESENTER DR. SUBRAHMANYAM BOYAPATI SYNOPSIS, IRELAND WHEN TUESDAY, 8 OCTOBER 8:40-9:40

#### ABSTRACT

This paper gives a review of the modeling and design of CMOS Miller operational amplifier (OpAmp) and folded cascode operational

amplifier that has high immunity to electro-magnetic interference (EMI). The highly EMI immune CMOS OpAmps and folded cascode OpAmps has unique features, such as compact power and low output offset voltage, when compared to the classical Miller OpAmp and the classical folded cascode OpAmps in the literature. The output offset current modeling equations are derived for the CMOS OpAmps including the body effect and channel length modulation. The CMOS OpAmps uses the replica concept along with the source-buffered technique in order to achieve high EMI immunity across a wide range of frequencies (10 MHz to 1 GHz). The highly EMI immune CMOS OpAmps are designed using the first-order quadratic mathematical model. The circuit has been fabricated/designed using 0.18  $\mu$ m mixed-mode CMOS OpAmps is less than 5 mV over a wide frequency range from 1 MHz to 1 GHz, which is lower when compared to the available classical Miller OpAmps and the folded cascode OpAmps.

#### PRESENTER'S BIOGRAPHY

Subrahmanyam Boyapati received the MTech. degree in integrated electronics and circuits from the Indian Institute of Technology (IIT), Delhi, New Delhi,India, in 2006, and the Ph.D. degree in microelectronics from the IITB-Monash Research Academy, IIT Bombay, Mumbai, India, in 2017. He is a recipient of the Prime Minister's Fellowship Scheme for Doctoral Research, a public–private partnership between the Science and Engineering Research Board, Department of Science and Technology, Government of India, and Confederation of Indian Industry. From 2018 to 2021, he was an Analog Design Engineer with Intel-Bangalore where he worked on high-speed receiver design for High Bandwidth Memory (HBM) applications. From 2001 to May 2024, he was a Key Researcher with the Center for Integrated Systems and Circuits Design, Carinthia University of Applied Sciences, Austria. Currently he is working as a Senior Staff Analog Design Engineer with Synopsys, Dublin, Ireland. His current research interests include analog and mixed signal integrated circuit design for sensor and biomedical applications, integrated circuit design with a high robustness to electromagnetic interference and high-speed receiver design circuits for the ADCs.

# #3: COMMON MODE NOISE REDUCTION METHODS USED FOR HIGH POWER DENSITY DC/DC CONVERTERS

PRESENTER **PROF. JUN IMAOKA** NAGOYA UNIVERSITY, JAPAN WHEN WEDNESDAY, 9 OCTOBER 8:40-9:40

#### ABSTRACT

Compound power semiconductor devices, such as Silicon Carbide (SiC) and Gallium Nitride (GaN), are widely adapted into automotive, renewable energy, and energy management applications to achieve carbon neutrality. These devices can operate at higher frequencies compared to Silicon (Si)-based devices due to their high switching speed and low on-resistance. Furthermore, high-frequency operation contributes to the realization of high power density in DC/DC converters. However, with the widespread application of compound semiconductor devices capable of high-frequency operation, the importance of common mode noise reduction based on a literature review. Primarily, this paper presents methods for common mode noise reduction in high-power and high-frequency applications without increasing the converter's volume.

#### PRESENTER'S BIOGRAPHY

JUN IMAOKA (Member, IEEE) received the M.S. and Ph.D. degrees in electronic function and system engineering from Shimane University, Matsue, Japan, in 2013 and 2015, respectively. From October 2015 to March 2018, he was an Assistant Professor with Kyushu University, Fukuoka, Japan. From April 2018 to March 2021, he was an Assistant Professor with Nagoya University, Nagoya, Japan. He is currently an Associate Professor with the Institute of Materials and Systems for Sustainability (IMaSS), Nagoya University. His research interests include the design of integrated magnetic components, modeling for high-power-density power converters, thermal management for power converters, magnetic material application, and EMI of switching power supply.

# TUTORIALS

### #1 IEC STANDARDIZED IC EMC TEST METHODS: APPLICATION GUIDANCE

#### PRESENTER DR. FRANK KLOTZ

WHEN

INFINEON TECHNOLOGIES - GERMANY MONDAY, 7 OCTOBER 12:30-14:00

#### ABSTRACT

The tutorial provides in the first part an overview of the current IEC EMC standards for integrated circuits, informs about ongoing and planned standardization projects and gives an outlook on the IC EMC standardization roadmap also with reference to relevant standardization activities in the automotive area at ISO and CISPR. The second part presents and discusses the approach and application of selected IC EMC measurement methods according to the Generic IC EMC Test Specification of the ZVEI.

#### PRESENTER'S BIOGRAPHY

Frank Klotz, studied electrical engineering at the Technical University of Ilmenau, where he received his PhD in the field of EMC of power semiconductor topologies. In 1996 he started his career in the semiconductor division of Siemens AG, now Infineon Technologies AG. Today he is head of Infineon's EMC organization, chair of IEC SC47A Integrated Circuits and member of the EMC standardization committees at IEC, CISPR and ISO

# #2 HOW SIGNAL AND POWER INTEGRITY INFLUENCE THE SILICON DEVICE INTEGRATION IN THE PACKAGE AND SYSTEM

PRESENTERS OLIVIER BAYET STMICROELECTRONICS GRENOBLE, FRANCE

AURORA SANNA STMICROELECTRONICS AGRATE BRIANZA, ITALY

TUESDAY, 8 OCTOBER 12:

12:30-14:00

#### ABSTRACT

In the context of integrated circuits development, signal and power integrity (SI & PI) optimization is key to ensure the required electrical performances. With the increasing operating frequencies, decreasing voltage levels and increasing power consumption, package interconnections assume a significant weight and the interaction between chip, package and board needs a deep assessment through a co-design and co-simulation approach. The proposed tutorial goes through the overall design process to optimize signal and power integrity, from pre-layout strategy definition to post-layout verification, with a strong focus on package interconnections technology and design. The importance of chip-package co-design is underlined and a constant link between design, electromagnetic modeling and simulations is maintained, to validate each step of the process.

#### Main topics:

- Pre-layout strategy for SI and PI optimization

- Die-package-board integration constraints

- Package technology selection based on physical and electrical constraints

- Design partitioning, smart routing strategy definition based on layout symmetries

- Layout optimization and verification for SI and PI

- Signal integrity simulations, from package-level to system-level

- Power integrity simulations, from package-level to system-level (DC and AC, frequency domain and time-domain, input models requirements, decoupling capacitors selection)

- Link between SI, PI and thermal for accurate analysis

- Link between SI/PI and electromagnetic emissions

- Output chip/package models

#### PRESENTERS' BIOGRAPHY

Olivier Bayet is Senior Member of Technical Staff at STMicroelectronics and has over 24 years of experience in design and EDA for IC and package. He developed new methods for voltage drop analysis, IC-package codesign and its associated physical and electrical verification. As part of the mobile platform and later networking processor design teams, Olivier setups the design and verification process for SoC-Package-PCB co-design to enable complex interfaces such as LPDDR, DDR, SerDes. Currently Olivier is leading the die/package co-design for various types of projects in the RF & Communication division of ST covering the signal integrity analysis of RF links, antennas, high speed serial links and the system power integrity analysis of low voltage and high-power consumption devices. Olivier holds an MSEE from ENSERB, Bordeaux, France.

Aurora Sanna got the master's degree in Electronics Engineering at Politecnico di Milano, in 2011. Since then, she has worked in the field of electrical modeling of interconnections, starting from PCBs and then moving to IC-packages, dealing with Signal Integrity, Power Integrity and Electromagnetic Compatibility problems. Currently, she is part of Back-end Manufacturing and Technology RnD group in STMicroelectronics and she is leader of a team dedicated to package design, electrical modeling and thermal modeling. She is member of STMicroelectronics Technical Staff.

# NETWORKING EVENTS

#### EGYPTIAN MUSEUM GUIDED TOUR

WHENTUESDAY, 8 OCTOBER, 17:00-18:00WHEREMUSEO EGIZIO<br/>VIA ACCADEMIA DELLE SCIENZE 6, 10123 TORINO

Enjoy a guided visit to Turin's top attraction, the Egyptian Museum, with priority tickets and no waiting in lines! Founded in 1824, it's the oldest and second most important after Cairo's. Discover the secrets and mysteries of ancient Egypt on this tour, from the writings of the Book of the Dead to fascinating amulets and daily life objects, including the magnificent Statuary. With over 30,000 items, the museum showcases 5,000 years of history through art, religion, and the era of the great pharaohs.

#### GALA DINNER

WHEN TUESDAY, 8 OCTOBER, 19:30

WHERE

ESPERIA RESTURANT Corso Moncalieri 2, 10131 Torino

In Turin, there is a special place—the historic building of the Società Canottieri Esperia, which houses the restaurant of the same name. It's a unique location in a privileged spot in the heart of the city, just steps away from the beautiful Piazza Vittorio Veneto. Here, you can enjoy lunch or dinner on the banks of the Po River. Designed in 1926 and inaugurated on December 2, 1928, the building feels more rural than urban. In the large main hall hangs a whale skeleton, a work by South American artist Juan Cespedes.

The 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits EMC COMPO 2024 October 7<sup>th</sup>-9<sup>th</sup>, 2024 Politecnico di Torino Torino, Italy

# TECHNICAL SESSIONS

#### TS#1: SUSCEPTIBILITY TO EMI OF ANALOG AND MIXED SIGNALS ICS

#### WHEN MONDAY, 7 OCTOBER, 10:10-12:10

SESSION CHAIRS

Prof. Sonia Ben Dhia, INSA de Toulouse, France

Prof. Jean-Michel Redouté, University of Liège, Belgium

#### Paper ID: #40

Characterisation of an EMI-Improved Integrated Folded Cascode Amplifier Structure Using the EMIRR Measurement Method

#### Author(s): <u>Dominik Zupan</u>, Nikolaus Czepl and Bernd Deutschmann (Graz University of Technology, Austria)

In this paper, we analyse the robustness of operational amplifiers (OpAmps) against electromagnetic interference (EMI). Therefore we compare a standard folded cascode amplifier structure with an EMI-improved amplifier structure introducing a cross-coupled double differential input pair. We perform measurements on the manufactured test chip structures to determine general characteristics (gain, offset, gain-bandwidth product (GBWP) and phase margin), as well as EMI-related characteristics (EMI-induced offset respectively electromagnetic interference rejection ratio (EMIRR)). Based on these characteristics, we compare both structures with regard to their performance. Further on, we put the measurements into relation with our previous findings that we obtained from simulation.

#### Paper ID: #10

Analysis of Operational Amplifier Susceptibility to Multifrequency Disturbance

Author(s): <u>Alexandre Boyer</u> (LAAS-CNRS, France); Fabrice Caignet (LAAS-CNRS & University of Toulouse, France)

This paper deals with the susceptibility of operational amplifiers (op-amps) in multifrequency injection. After an indepth analysis of the different failure mechanisms that induces DC-offset based on experimental results on a generalpurpose op-amp, the paper proposes a risk assessment method based on continuous wave susceptibility test results.

#### Paper ID: #26

#### Analyzing and Modeling of the Susceptibility to Temporary Malfunction in Automatic Gain Control Loops

Author(s): <u>Tom Billaux</u> (University of Montpellier, IES, France); Jérémy Raoult (Université Montpellier 2, France); Patrick Hoffmann (CEA, France)

The paper presents a study of the dynamic response of an Automatic Gain Control (AGC) loop exposed to a pulsed radiofrequency intentional interference. The influence of the various parameters of the pulse on its behavior is investigated, and a comprehensive model replicating the observed effects is presented. It is demonstrated that the pulse duration optimizing the susceptibility studied here is directly linked to the settling time of the AGC.

The 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits

10:30-10:50

10:10-10:30

10:50-11:10

EMC COMPO 2024 October 7th-9th, 2024 Politecnico di Torino Torino, Italy

### Paper ID: #33 Evaluation of Ground Terminal Against Noise by Direct Power Injection Method

Author(s): Takashi Nomura (DENSO, Japan); Mitsuhiro Hasegawa and Ko Oyama (Denso Corporation, Japan); Yosuke Kondo (DENSO Corporation, Japan); Koji Ichikawa (Nagoya Institute of Technology, Japan)

This paper shows that the immunity characteristics of integrated circuits (ICs) having large number of terminals to be evaluated can be evaluated macroscopically by measuring the strength against the noise of the ground terminal. A voltage reference circuit was fabricated in siliconon- insulator Bipolar/CMOS/LDMOS (SOI-BCD) process [8], and the strength against the noise of power supply terminals and the ground terminal were compared. The strength was measured by direct power injection (DPI) method [1] at each terminal. The reference potential for applying noise to the ground terminal was a potential in a no element region separated from the circuit region by an insulator. As a result, it was confirmed that the strength against the noise of the ground terminal was same with the low strength of other terminals. In addition, similar results were obtained by a simulation.

### EMI Immunity of the Nauta Inverter-Based Amplifier

### Author(s): Andrea Rosa, Anna Richelli and Luigi Colalongo (University of Brescia, Italy)

This paper investigates the effect of Electromagnetic Interferences (EMI) on inverter-based analog amplifiers, as the Nauta operational transconductance amplifier (OTA). We show that, thanks to the their simple circuital topology that does not include current mirrors and differential pair, the inverter-based analog amplifiers have a much higher EMI immunity respect to the classical topologies: about one order of magnitude.

#### Paper ID: #11

Paper ID: #9

#### System-On-Chip Preventing Discharge of Bootstrap Capacitor of High-Side Drivers

Author(s): Kamel Abouda (Emc Ic Expert, USA); Matthew Bacchi (NXP Semiconductors Toulouse, France)

Integrated high-side switches are omnipresent in automotive integrated circuits (airbags, power control units, alternator regulators, window lift applications, injectors control...). In non-SOI technologies, parasitic NPN and PNP transistors can degrade IC performance especially when EMC or ESD disturbances are applied to the circuit. This paper presents a small system on chip solution providing remarkably high EMC/ESD susceptibility performance for high-side switch drivers while increasing IC performance during normal operation using a wide range of external components.

11:10-11:30

11:30-11:50

11:50-12:10

#### TS#2: MEASUREMENT METHODS FOR CHIP LEVEL EMC

#### WHEN MONDAY, 7 OCTOBER, 14:00-16:00

SESSION CHAIRS

# RS Prof. Hyun Ho Park, The University of Suwon, South Korea Prof. Alexandre Boyer, INSA de Toulouse, France

#### Paper ID: #34

#### Butterfly Probes: Estimating the Derivative of the Magnetic Flux

Author(s): Philippe Maurine (LIRMM, Montpellier University, France); Jérémy Raoult and <u>Anselme Mouette</u> (University of Montpellier, France); Julien Toulemont (ANSSI, France)

The main way to increase the spatial selectivity of near field probes has been to make coils with smaller and smaller diameters. This is especially true for secure applications (sidechannel attacks). In this paper, we investigate an alternative way with secure applications in mind. It consists in designing probes that measure the spatial derivative of the magnetic flux instead of the flux itself. The paper presents the motivation, the concept and preliminary results obtained with a first prototype.

#### Paper ID: #35

#### Influence of Sensing Resistor on IC-Level Noise Measurement of DC-DC Converters by 1 $\Omega$ Method

Author(s): <u>Hyun Ho Park</u> (The University of Suwon, Korea (South)); Jiseong Kim (KAIST, Korea (South)); Eakhwan Song (Kwangwoon University, Korea (South)); Hongseok Kim (CPS Tech, Inc., Korea (South)); Sangho Cho (LG Electronics Inc., Korea (South))

This paper presents a method for determining the appropriate sensing resistance value when measuring integrated circuit (IC) noise in DC-DC converter ICs using the  $1\Omega$  method as outlined in IEC 61967-4. By modeling the DC-DC converter circuit as an equivalent RLC resonance loop and accounting for the parasitic inductance of the sensing resistor, we established the permissible range for the sensing resistance. Through circuit simulations, this study examines the impact of sensing resistance and parasitic inductance on the ringing noise of DC-DC converter ICs, ultimately determining the optimal resistance value for accurate IC-level noise measurement.

#### Paper ID: #27

#### 14:40-15:00

#### Near Field Scan Investigation Method to Reduce 4.8GHz Emission on a BLE Application

Author(s): <u>Jeremy Ruau</u>, Bertrand Vrignon and Christophe Menard (NXP Semiconductors, France); Lucy Liu (NXP Semiconductors, China); Matthieu Baudry (NXP Semiconductors, France)

The product studied is a low-power, highly secure, single-chip wireless MCU that integrates high-performance Bluetooth Low Energy for Automotive and Industrial applications. During EMC radiated emission test, a peak appeared around 4.8 GHz, due to 2nd harmonic of BLE. EMC lab proposed new investigation method based on near field scan to analyse the peak and try to improve the emission level. This work aims to first understand the origin of the 4.8 GHz peak encounter in RE measurement, then to explain the importance of a good antenna matching network at high frequency and finally to detail the solution found to reduce the emission level.

> The 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits

14:00-14:20

14:20-14:40

Paper ID: #28

15:00-15:20

#### Design and Application of RFIC Detector: To Measure Coupled Power Into IC Pin via PCB Trace

Author(s): <u>Arunkumar Hunasanahalli Venkateshaiah</u>, John F Dawson, Martin Trefzer, Simon Bale, Andy Marvin and Martin Robinson (University of York, United Kingdom (Great Britain))

In this paper, we discuss the design of an RF IC detector with eight channels connected to the package pins, designed to determine the incident RF power on each pin. Some of these channels possess different sensitivity levels based on the amplification circuit block they use. A PCB test bench with test tracks has been designed to allow the measurement of RF power coupled to the detector IC pins when illuminated by a RF source. Our discussion will also encompass the applications of the RF IC detector in detecting stochastic EM fields in reverberant or equivalent real-world environments. The key contribution in this paper is the design of RF IC detector which has these applications.

#### Paper ID: #17

15:20-15:40

#### On-Chip ESD Current Sensor for Nanosecond Oscillation Waveform Over Ampere Detecting

Author(s): <u>Kazuki Shimada</u> (Renesas Electronics Corporation, Japan); Mototsugu Okushima (Industry of ESD & Renesas Electronics Corporation, Japan)

To analyze IC destruction and malfunction due to ESD (IEC61000-4-2), we proposed an on-chip current sensor that can accurately capture the entire ESD current waveform flowing into the IC that oscillates significantly for positive and negative in the nanosecond range. Measurement accuracy has improved by compensating for measurement errors caused by voltage overshoot in the nanosecond range of the current detection device. The ESD current waveform flowing into the IC is different from the standardization waveform, and a positive and negative oscillation waveform can come in, and we have designed to handle these polarities. This sensor sets a design window that does not incorrectly respond against noise that does not affect the system, and it only captures ESD currents of ampere or more. This sensor will become an important component for analyzing IC destruction and malfunction due to ESD.

#### Paper ID: #50

15:40-16:00

Accelerated Characterisation of Operational Amplifiers' Susceptibility Using Multitone Disturbance

Author(s): <u>Matthieu Laidet</u> (LAAS CNRS & EDF Power Network Lab, France); Alexandre Boyer (LAAS-CNRS, France); Sonia Ben Dhia (INSA de Toulouse, France); Julien Gazave (EDF Group, France)

This paper presents an original approach to accel- erate susceptibility testing of Operational Amplifiers (op-amp), using large band multitone signals, for a Direct Power Injection (DPI) setup. The relation between Continuous Wave (CW) and multitone susceptibility results, the associated limits and the global characterisation flow are discussed.

#### WHEN MONDAY, 7 OCTOBER, 16:20-18:20

SESSION CHAIRS

Prof. Etienne Sicard, INSA de Toulouse, France Dr. Sergey Miropolsky, Infineon Technologies AG, Germany

#### Paper ID: #47

16:20-16:40

Inspection Tools for Gaussian Process Regression Modeling of Electromagnetic Fields of Electronic Boards and Chips

Author(s): <u>Tomas Monopoli</u>, Xinglong Wu and Sergio A Pignari (Politecnico di Milano, Italy); Karl-Friedrich J Wolf (European Space Agency (ESA) & ESTEC, The Netherlands); Flavia Grassi (Politecnico di Milano, Italy)

Gaussian Process Regression (GPR) has emerged as a powerful technique for building surrogate models of electromagnetic field scans in electronic systems. However, standard GPR models often struggle to capture the nonisotropic and complex spatial patterns commonly found in electronic board field distributions. In this paper, we propose some inspection tools to analyze the underlying correlation structure in the measurement data. This analysis is demonstrated by considering as input data the near field emissions from a bent miscrostrip line (full-wave simulations) and a chip (near-field measurements).

#### Paper ID: #12

16:40-17:00

#### An ICIM-CI Model for Mass Production Development Considering Manufacturing Variations

Author(s): <u>Hidetake Sugo</u> (DENSO CORP., Japan); Norimasa Oka (DENSO COPR., Japan); Takaya Nagai, Koji Hattori and Takeshi Matsuzaki (DENSO CORP., Japan)

An ICIM-CI model of an analog circuit with a differential amplification for mass production development is proposed. It is observed that manufacturing variations, such as in terms of the oscillation frequency, cause differences in failure thresholds, obtained by the DPI method, between samples. The maximum difference is 8.7 dB at 1.0 MHz. To predict the lowest forward power that causes failure, a prediction formula based on design information is obtained. By comparing the prediction results with measurements, it is confirmed that the forward power can be estimated within the range of variations.

#### Paper ID: #39

17:00-17:20

#### A Case Study for the EMC Co-Simulation of Injection Path Model Using WR Method

Author(s): <u>Md Moktarul Alam</u> (ESEO, France); Richard Perdriau and Mohamed Ramdani (ESEO, France); Mohsen Koohestani (ESEO School of Engineering & IETR, University of Rennes, France)

This article highlights an assessment of the cosimulation suitability to evaluate the conducted electromagnetic immunity of an injection path model between two source circuits using waveform relaxation (WR). The latter enhances co-simulation performance and stability by adjusting the impedance approximation parameter variables with the voltage and current control sources. Additionally, this paper emphasizes the significance of parameter initialization to interface for the defined subsystems and ensures compatibility with the overall system. Testing is conducted on an injection path model circuit with an input pulse voltage source from 0 to 2.5 V. A comparative analysis with the WR method indicates output voltage difference of less than 1.4% between the full system values after three iterations only. These results highlight the proposed method's ability to achieve faster and more accurate convergence compared to the traditional WR methods.

#### Paper ID: #24

17:20-17:40

#### A Simulation Workflow for Predicting IC Stripline Radiated Emissions of Bond Wire-Based Systems

# Author(s): <u>Dominik Kreindl</u> (Ams-OSRAM AG & Graz University of Technology, Austria); Bernhard Weiss and Christian Stockreiter (Ams-OSRAM AG, Austria); Thomas Bauernfeind and Manfred Kaltenbacher (Graz University of Technology, Austria)

Light sources in optical sensor packages can cause high levels of electromagnetic interference due to their high current consumption and short switching times. The radiating structures are electrically short for the frequency range of interest for metrological verification according to the IEC 61967-8 standard. This can be used to find an equivalent representation of the emission sources in terms of Hertzian dipole moments. This paper presents a purely analytical simulation workflow for predicting radiated emissions in IC stripline measurements by employing dipole moments. The procedure is evaluated against finite element simulations and measurement data. The results show promising correlations in the lower frequency range, but significant deviations are observed above 1.5 GHz. Further research is needed to identify the root cause of these deviations.

#### Paper ID: #30

#### 17:40-18:00

Enhancing High-Speed Ethernet Link Design at 25 Gbps in Aerospace Environments Through Optimization Algorithms

#### Author(s): <u>Soazig Le Bihan</u> (Thales & Laboratoire IMS, France); Tristan Dubois (Laboratoire IMS, France); Jean-Baptiste Begueret (University of Bordeaux I, France); ADIL El Abbazi (Thales AVS, France)

Introducing a new high-speed design requires a careful optimization of any discontinuities that may degrade signal quality. A high-speed signal includes structures such as BGA (Ball Grid Array), vias, AC coupling capacitors, or connectors. Poorly matched impedance may result in undesirable signal reflections, energy losses, and electromagnetic interference. These structures need to be wisely optimized in order to limit signal reflections along the path while taking into account manufacturing constraints, costs, performance and routing density for avionics products. However, with each new design change during the various stages of development, major modifications can challenge previous optimization choices. Therefore, it is crucial to create adaptive and flexible models that can easily evolve with these changes. The objective is to develop a library of optimized models that can be seamlessly integrated into internal routing tools and efficiently reused for future designs. Three types of mathematical algorithms were studied based on the objectives, constraints, performance, and time required to converge toward the best design in order to automate this time-consuming process.

#### Paper ID: #21

#### 18:00-18:20

#### High-Fidelity S-Parameter Prediction Using Transfer Learning Based Encoder-Decoder Model

Author(s): Ruiqi Dai, Yuhao Xu, <u>Jiarui Qiu</u>, Hanzhi Ma and Er-Ping Li (Zhejiang University, China)

The demand for large-scale data samples has always been a significant bottleneck in the application of artificial intelligence methods in the field of electromagnetic compatibility (EMC) of integrated circuit (IC). This paper proposes the Transfer Learning Encoder-Decoder network (TL-ED) method for predicting circuit S-parameters. Considering the high computational cost involved in obtaining accurate high-fidelity data samples, this method utilizes transfer learning to transfer the rough model, which is modeled based on low-fidelity data with low computational costs, to the accurate model. Subsequently, the model is fine-tuned using a small amount of high-fidelity data. Application results confirm that this approach significantly reduces the demand for high-fidelity data and has the potential to be applied in IC-EMC analysis where data acquisition through testing experiments is necessary.

#### TS#4: EMC-AWARE DESIGN OF ICS AND GUIDELINES

#### WHEN TUESDAY, 8 OCTOBER, 10:10-12:10

SESSION CHAIRS Dr. Kamel Abouda, NXP Semiconductors, France Prof. Bernd Deutschmann, Graz University of Technology, Austria

#### Paper ID: #63

10:10-10:30

10:30-10:50

EMI Robust Comparator Design for Protection Features of Smart Power Switches

Author(s): <u>Daniel Kircher</u> (Graz University of Technology, Austria); Cristian Ionascu (Infineon Technologies Austria AG, Austria); Bernd Deutschmann (Graz University of Technology, Austria)

In the field of automotive smart power switches, the integrity of the chip's temperature signal processing and overtemperature recognition are critical. This paper presents a robust input stage for a comparator designed to withstand electromagnetic interference (EMI) while maintaining accuracy. We present a novel design that incorporates hysteresis and uses linearisation techniques to enhance immunity to radio frequency (RF) interference. Our results show a significant improvement in the electromagnetic immunity of the overtemperature protection mechanism. We validate our results with direct power injection (DPI) simulations comparing the standard input topology with the EMI improved one.

#### Paper ID: #25

#### STT-MRAM Based ESD and EFT Immunity Analysis

Author(s): Jianfei Wu (National University of Defense Technology, China); <u>Yanfang Lu</u>, Yang Li and Hongli Zhang (Tianjin Institute of Advanced Technology, China); Yiming Zhang (Hebei University of Technology, China); Xing Zhao (Institute of Microelectronics of Chinese Academy of Sciences, China); Wei Zhu (Research Institute of Integrated Circuits and Systems Application, China)

This study analyses the Electromagnetic Immunity (EMI) of STT-MRAM. By exhaustively exploring and verifying the Electrostatic discharge (ESD) and Electrical Fast Transient (EFT) of STT-MRAM, the impact of ESD and EFT on the performance of STT-MRAM is investigated, the potential threat of transient electromagnetic interference to STT-MRAM memory is revealed, and suggestions are made to improve its electromagnetic compatibility (EMC), which provides an important reference for its reliable application.

#### Paper ID: #41

10:50-11:10

Comprehensive Study of EMI Effects on Wireline Transceiver Systems: A Review of Silicon-Proven Techniques

Author(s): Mohit Singh Choudhary (Indian Institute of Technology, Bombay, India); <u>Jean-Michel Redouté</u> (University of Liège, Belgium); Maryam Shojaei Baghini (Indian Institute of Technology, Bombay)

This research paper provides an extensive examination of electromagnetic interference (EMI) in wireline transceiver systems. Wireline transceiver circuits are particularly susceptible to undesired electromagnetic waves in their environment. The paper delves into a mathematical approach for incorporating EMI into circuit simulation tools. Additionally, it explores the impact of EMI on different wireline communication systems, such as LVDS, CML, and PAM-4 transceiver systems. The goal is to comprehensively understand how EMI affects the performance of these wireline communication systems.

#### Paper ID: #49

#### 11:10-11:30

#### Evaluation of the Electromagnetic Emission of ICs Using Different Spread Spectrum Approaches

#### Author(s): Marco Pfeifer, Ko Odreitz and Bernd Deutschmann (Graz University of Technology, Austria)

This paper examines the use of spread spectrum clocking approaches to reduce the increasing electromagnetic emissions caused by the constantly rising switching frequencies of modern electronic systems. The approach to reducing these emissions is based on spreading the spectral power of a narrowband signal over a certain bandwidth in order to reduce the peak amplitude. We will compare the performance of a spread spectrum clock generator based on the random method with one using simple frequency modulation with a triangular modulation signal and relate it to their theoretical behavior. Furthermore, we will perform CISPR-compliant emission measurements with different detectors of an EMI receiver and compare the influence on the measurement results.

#### Paper ID: #14

#### 11:30-11:50

#### Effects of Ionizing Radiation on the EMI-Induced Offset Voltage of Operational Amplifiers

# Author(s): <u>Nikolaus Czepl</u>, Dominik Zupan, Alicja Michalowska-Forsyth and Bernd Deutschmann (Graz University of Technology, Austria)

In this work, we investigate the impact of ionising radiation on the robustness towards electromagnetic interference (EMI) of operational amplifiers (OpAmps). Therefore we irradiate two OpAmps, one including a standard differential input stage structure, the other OpAmp featuring a second crosscoupled double differential input pair added to the standard input stage structure. We perform measurements on the manufactured test chip structures to determine general characteristics (gain, offset, gain-bandwidth product (GBWP) and phase margin), as well as EMI-related characteristics like EMI-induced offset and electromagnetic interference rejection ratio (EMIRR). Based on these characteristics, we compare both structures with regard to their performance prior to, during and after irradiation with X-rays. We observe a change in the EMIRR performance with increasing ionising dose. Finally, we explain our observations by taking into account transistor-level effects.

#### Paper ID: #57

#### 11:50-12:10

#### Accuracy of GPS Positioning Measurements in Response to Electromagnetic Noise Characteristics

# Author(s): <u>Hiraku Uehara</u> (Kobe University, Japan); Koh Watanabe (National Institute of Information and Communications Technology, Japan); Sosuke Ashida, Yushi Mitsuya, Satoshi Tanaka and Makoto Nagata (Kobe University, Japan)

Autonomous vehicles, such as unmanned aerial vehicles (UAV) and self-driving cars, have been recently deployed. Many of them use a global positioning system (GPS) to acquire location data, which requires high accuracy. On the other hand, the electromagnetic (EM) environment inside the autonomous vehicle is prone to electromagnetic interference (EMI) between EM noise and GPS signals, and there is a risk that this EMI inside the autonomous vehicle may deteriorate the accuracy of GPS positioning measurements. Previous studies have reported the interference of EM noise from UAVs with global navigation satellite system (GNSS) and with mobile communications. Evaluations and countermeasures for the EMI problems are necessary since the low accuracy of positioning measurements may lead to malfunctions and accidents. This study showed the accuracy of positioning measurements under two EM noise components, which are experimented with the EMI of EM noise to GPS signal with a GPS receiver module. As a result, we found that the characteristics of EMI were dependent on EM noise components, specifically, random noise and harmonic noise.

### TS#5: SUSCEPTIBILITY OF ICS TO INTENTIONAL EMI AND ESD

#### WHEN TUESDAY, 8 OCTOBER, 14:00-16:00

#### SESSION CHAIRS

Dr. Wolfgang Wilkening, Robert Bosch AG, Germany Prof. Makoto Nagata, Kobe University, Japan

#### Paper ID: #29

#### Assessing IEMI Vulnerabilities in MEMS Barometers: A Comparative Approach

# Author(s): <u>Louis Cesbron Lavau</u> (RWTH Aachen & Fraunhofer INT, Germany); Michael Suhrke (Fraunhofer INT, Germany); Peter Knott (Fraunhofer FHR, Germany)

As the Internet of Things (IoT) expands, sensors play a crucial role in collecting and transmitting vital data across various domains. However, their susceptibility to Intentional Electromagnetic Interference (IEMI) raises significant concerns. This paper investigates the vulnerabilities of barometric sensors to IEMI. Utilizing a methodology similar to previous studies, measurements were conducted using Continuous Wave (CW) and pulse signals to assess sensor behavior under IEMI. The findings reveal differences in susceptibility between the studied barometers highlighting distinct vulnerabilities and responses to electromagnetic interference. Specifically, variations in temperature and pressure readings, along with system crashes induced by IEMI, were observed. Additionally, potential coupling paths on PCBs are discussed. This study underscores the importance of tailored mitigation strategies for sensor-based systems.

#### Paper ID: #16

# Susceptibility of an Analog Temperature Measurement Function: First Step to Optimize the IEMI Waveform

Author(s): <u>Antoine Duquet</u> (University of Bordeaux & Thales SIX, France); Tristan Dubois (IMS BORDEAUX, France); Genevieve Duchamp (IMS, France); David Hardy and Franck Salvador (Thales SIX, France)

This contribution deals with the electromagnetic susceptibility of an electronic function based on the susceptibility of its components. The susceptibility of the electronic function has been measured and modeled from its components' susceptibility characterizations. The function has been subjected to some modulated interferences to observe its susceptibility behaviors and vulnerabilities.

#### Paper ID: #62

#### Controlling Faulty Byte Outputs With IEMI Against Cryptographic ICs

Author(s): <u>Hikaru Nishiyama</u> (National Institute of Advanced Industrial Science and Technology (AIST) & Nara Institute of Science and Technology (NAIST), Japan); Daisuke Fujimoto and Yuichi Hayashi (Nara Institute of Science and Technology, Japan)

Intentional electromagnetic interference (IEMI) for cryptographic integrated circuit (IC) has been reported as a threat for fault injection attack that extracts secret key information by inducing temporary fault in a specific number of bytes in the cryptographic process. And the previous studies on IEMI fault injection have focused on whether it is possible to generate only 1-byte fault, which is necessary for Piret's Differential Fault Analysis (DFA), a secret key analysis method.

> The 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits

28

#### 14:40-15:00

14:20-14:40

14:00-14:20

On the other hand, some methods have been proposed that use multiple-byte faults to enable secret key analysis even under attack conditions where DFA is difficult to apply. If multiplebyte faults that are applicable to such analysis methods can be generated, the threat of IEMI fault injection may increase. In this paper, we show that the number of faulty bytes can be precisely controlled by varying the parameter of the EM waves injected to the cryptographic IC with high resolution, and that the faults output by IEMI fault injection can be used for analysis methods other than DFA. Specifically, we use impulses as the EM waves, measure the electrical changes that occur in the cryptographic IC when the amplitude and pulse width are manipulated, and investigate the relationship between the number of faulty bytes and the electrical changes.

#### Paper ID: #67

#### Modeling and Analysis of On-Chip Voltage Fluctuations Caused by Electromagnetic Fault Injection

Author(s): Takuya Wadatsumi, Rikuu Hasegawa, Kazuki Monta and Takuji Miki (Kobe University, Japan); Lang Lin and Norman Chang (ANSYS, Inc., USA); <u>Makoto Nagata</u> (Kobe University, Japan)

Near-field electromagnetic fault injection (EMFI) is one of the most commonly used attack methods to intentionally cause errors in digital circuits due to its inherent advantages. A full-wave simulator was used to analyze the voltage fluctuations on the on-chip power mesh excited by EMFI. We have described the relationship in which the shape of the voltage fluctuations on the power mesh inside ICs is derived from the differentiation of the current flowing through the injection coil by using Maxwell's equations and full-wave simulations. In addition, the results with different injection positions and ideal voltage source points have showed that the areas of high sensitivity vary on the power supply mesh.

#### Paper ID: #55

#### Analysis, Testing and Comparison of Different Commercial ESD Detectors

Author(s): <u>Musab Hameed</u>, Abraham Reithofer and Gabriel Fellner (Graz University of Technology, Austria); Ahmad Hosseinbeig (Apple, USA); David Pommerenke (TU Graz, Austria)

This paper investigates the response of various commercial electrostatic discharge (ESD) detectors with respect to their ability to detect charged device model (CDM) like short pulses and their ability to discriminate between CDM and non-CDM pulses. A series of test setups (TEM cell, sphere-to-Gnd discharge, narrow pulse generator) were set up to evaluate how different detectors behave at different pulse widths and field strengths. Pulse durations varying from 150 ps - 16 ns FWHM were applied in the different test setups. The measured responses of the detectors under different ESD conditions are analyzed and compared.

#### Paper ID: #44

#### 15:40-16:00

#### Functional Failures in a Sensor Application Caused by System-Level ESD

#### Author(s): <u>Stefan Jahn</u> (Infineon Technologies AG, Germany)

This paper reports the functional behavior of a system consisting of a pressure sensor within its sensor module, a twowire supply with current modulated communication channel and an electronic control unit equivalent during powered system-level ESD tests. It discusses functional recoverable soft-failures, their failure mechanisms and root causes considering overall system properties as well as special electro-mechanical integrated circuit properties, and ESD test requirement and procedures.

> The 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits

#### 15:00-15:20

# 15:20-15:40

#### WHEN WEDNESDAY, 9 OCTOBER, 10:10-12:10

SESSION CHAIRS Prof. Jun Imaoka, Nagoya University, Japan Dr. Erica Raviola, Politecnico di Torino, Italy

#### Paper ID: #42

Passive DC-Input and DC-Input/AC-Output EMI Filter for DC-AC Inverter

Author(s): <u>Matthias Schulz</u> and Michael Kopf (Siemens AG, Germany)

This paper aims to compare the performance of an electromagnetic interference (EMI) direct current (DC)-input filter with a combined DC-input/alternating current (AC)-output filter. The EMI filters will be implemented in a DC-AC inverter to comply with regulatory standards. The DC-AC inverter has a two-level topology, with a defined switching frequency of 4 kHz. A theoretical model of the entire system, including the considered parasitic elements for cables, DC-AC inverter, and motor, is presented. Single-phase equivalent circuits for common mode (CM) and differential mode (DM) noises are derived from this circuit. The required transfer function to fulfill the standards for the two-level inverter is used to evaluate the influence of the EMI filter components and necessary filter stages. To accomplish this, the noise spectrum of the two-level topology without any EMI measures and the limit lines of two different regulatory standards are utilized. Considering this perspective, the passive components of the EMI filters are selected, with separate investigations conducted on CM and DM noises. Finally, conducted EMI measurements on a 55 kW DC-AC inverter prototype validate the proposed filter damping. Deviations between measured noise and the expected damping are discussed in detail.

#### Paper ID: #60

10:30-10:50

A Comparison of Spread Spectrum and Sigma Delta Modulations to Mitigate Conducted EMI in GaN-Based DC-DC Converters

#### Author(s): <u>Alberto Barbaro</u>, Markeljan Fishta, Erica Raviola and Franco Fiori (Politecnico di Torino, Italy)

GaN power transistors offer significant advantages with respect to Si ones, but introduce challenges in meeting EMC regulations due to their high switching frequencies. This paper compares two modulation schemes, Spread-Spectrum Modulation (SSM) and Sigma-Delta Modulation ( $\Sigma\Delta M$ ), for reducing the conducted Electromagnetic Interference (EMI) delivered by GaN-based DC-DC converters. The study analyzes how these techniques impact converter performance and evaluates their effectiveness in reducing conducted EMI at low frequencies. The findings provide valuable insights for designers seeking the most effective strategy for EMI mitigation.

#### Paper ID: #37

#### DM EMI Noise Prediction for BCM Based Single-Phase Grid-Connected Inverter

#### Author(s): <u>Chen Liu</u>, Freede Blaabjerg and Pooya Davari (Aalborg University, Denmark)

Boundary conduction mode (BCM) current control is an emerging soft-switching technique in single-phase gridconnected inverters. However, the significant ripple in inductor current leads to heightened electromagnetic interference (EMI) noise in form of differential mode (DM) noise. This paper proposes an analytical model to predict the differential mode EMI noise for BCM based single-phase grid-connected inverter, which can facilitate the design of the

> The 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits

10:50-11:10

10:10-10:30

EMI filter without repetitive measurements. Experimental validation is conducted on a 500 W hardware prototype to affirm the feasibility and efficacy of the proposed model.

#### Paper ID: #61

#### 11:10-11:30

#### A Critical Analysis of Amplifier Requirements in Capacitance-Boosting Circuits for EMI Reduction

#### Author(s): <u>Markeljan Fishta</u>, Pietro Montorsi and Franco Fiori (Politecnico di Torino, Italy)

This work presents a critical analysis of the amplifier requirements for capacitance-boosting circuits, like those used in active EMI filters. The relationship between the amplifier specifications and the overall performance of these circuits is investigated. The study begins with an overview of the fundamental principles of capacitance-boosting circuits, followed by an in-depth exploration of the role of amplifiers in these systems. Then, various amplifier parameters such as bandwidth, output impedance, and output swing are critically analyzed, highlighting their impact on the performance of capacitance-boosting circuits. Through rigorous theoretical analysis and computer simulations, this work provides valuable insights into the optimal amplifier requirements for capacitance-boosting circuits.

#### Paper ID: #69

#### 11:30-11:50

Analysis of Partial RF Emission Spectra of IC Functions and Subcircuits on the Example of Power Switch ICs

#### Author(s): <u>Sergey Miropolsky</u> and Frank Klotz (Infineon Technologies, Germany)

This paper presents a simulation based approach to decompose the overall conducted RF emission of a complex integrated circuit (IC) into partial emission spectra due to various functional blocks or processes in the analyzed DUT IC. The approach is described based on a generic power switch.

#### Paper ID: #36

#### 11:50-12:10

#### Measurement of PCB-Related Commutation-Loop Inductance Using a Vector Network Analyzer

#### Author(s): <u>Maurizio Tranchero</u> (Ideas & Motion, Italy); Marco Garelli (Keysight Italy Srl, Italy)

The stray inductance in the commutation loop is cause of oscillations that affect the efficiency of a power converter and are source of electromagnetic noise. Since the advent of Wide Band-Gap (WBG) power devices made possible generating steeper current and voltage transition, these high-speed switching is exacerbating the phenomenon. Commercial components are characterized by the manufacturers and datasheets are often reporting the value of the stray inductance for a given package. Unfortunately this is not enough, since the Printed Circuit Board (PCB) introduces the main part of the commutation loop inductance. This paper proposes to use Vector Network Analyzer (VNA) measurements to characterize the impedance of a bare PCB trace. The presented method has proved to be reliable in comparing different PCB designs to determine the best one.

#### WHEN WEDNESDAY, 9 OCTOBER, 13:40-16:00

#### SESSION CHAIRS Prof. Francesco de Paulis, Università degli Studi dell'Aquila, Italy Prof. Flavia Grassi, Politecnico di Milano, Italy

#### Paper ID: #46

# Automated Method to Synthesize RLCK-Circuits From S-Parameters

Author(s): <u>Alexander Schade</u> (Infineon Technologies AG Neubiberg, Germany); Frank Klotz (Infineon Technologies, Germany); Robert Weigel (Friedrich-Alexander Universität Erlangen-Nürnberg, Germany)

To understand and control parasitic elements on the PCB-, package- and chip-level, designers require compact yet precise circuit models. The PEEC methods and "classical" parasitic extraction exhibit distinct disadvantages when applied to systems comprising layered planar conductors: Due to their reliance on partial inductances, the resulting models are not very intelligible and comparably complex. In contrast, our approach synthesizes highly compact and interpretable circuits based on loop inductances. Our novel method is more general than the algorithm by YOUNG. At the core of our technique is an exact equivalent circuit of multi-port S-parameters, applicable also to electrically large systems and radiation coupling.

#### Paper ID: #48

#### Loop Inductance Based RLCK Models of PCBs and IC-Packages in Practice

Author(s): <u>Alexander Schade</u> (Infineon Technologies AG Neubiberg, Germany); Frank Klotz (Infineon Technologies, Germany); Robert Weigel (Friedrich-Alexander Universität Erlangen-Nürnberg, Germany)

Loop inductances offer decisive advantages over partial inductances when electromagnetic systems shall be modeled in a compact and understandable manner. This publication builds on a previously published mathematical technique to extract physical "white-box" models from S-parameters of systems comprising, e.g., power IC metallization, interposers, ICpackages, PCBs and an environment. We shown how a complex system can be segmented by means of differential source and sink ports, forming a multigraph. The ports should be arranged in order to minimize the number of large magnetic couplings by reducing loop area and overlap. We discuss practical examples, such as striplines, half bridges, discrete coils and segmented ground planes. The technique supports development of CMOS SoCs, integrated Automotive ICs, fast-switching DC/DC-converters and high-power modules (SiC MOSFETs, GaN HEMTs).

#### Paper ID: #64

#### Suppression of Power Distribution Network PCB-Package Resonance for Low Target Impedance

Author(s): <u>Francesco de Paulis</u> (University of L'Aquila, Italy); Faye Squires (Missouri University of Science and Technology, USA); Yifan Ding (Missouri UNiversity of Science and Technology, USA); Matteo Cocchini, Matthew Doyle and Samuel Connor (IBM Corporation, USA); Albert Ruehli (Missouri University of Science and Tech, Jordan); Chulsoon Hwang (Missouri University of Science and Technology, USA); Lijun Jiang (Missouri University of Science and Technology, USA & EMC Lab, USA)

The suppression of the large resonance peak that may appear due to the equivalent parallel circuit between the package capacitance and PCB inductance is discussed. Such resonance may be amplified if the decoupling capacitors are not appropriately selected. The relevant parameters involved in the PDN design and a feasible solution strategy are

The 14th International Workshop on the Electromagnetic Compatibility of Integrated Circuits

14:20-14:40

13:40-14:00

14:00-14:20

presented based on the identification of a simplified equivalent circuit that is able to replicate the resonant behavior. The optimization of the relevant parameters of such circuit are able to suggest the best strategy for identifying the decoupling capacitors with appropriate values of parasitic inductance and resistance.

#### Paper ID: #66

#### 14:40-15:00

#### Investigation on the Effect of Different Form Factors on the Performance of Miniaturized Transformers

Author(s): Simone Negri, Xiaokang Liu, Giordano Spadacini, <u>Flavia Grassi</u> and Sergio A Pignari (Politecnico di Milano, Italy); Aurora Sanna and Damian Halicki (STMicroelectronics, Italy)

Miniaturized transformers have become essential components to enable the realization of compact, efficient, and costeffective electronics systems. Depending on the selected substrate and technology, planar micro-transformers can be integrated directly on a silicon device, included as stand-alone components in a System-in-Package (SiP) approach, or mounted directly on PCB. In this paper, an investigation on the effect of different form factors, defined as the ratio between the shorter and longer substrate sides, on the performance of miniaturized transformers is presented. Relevant performance indicators are defined, and a test case is numerically analysed, varying the form factor from 1 to 0.46, with 0.01 steps. The presented results show marginal variations on both voltage ratio and efficiency for form factors ranging from 1 to 0.8, while potentially severe reduction in efficiency up to 10 % can be expected for form factors smaller than 0.5.

#### Paper ID: #15

#### 15:00-15:20

#### Reconfigurable Board-To-Board Interconnect Utilizing Bistable Compliant Ribbon Wires

Author(s): <u>Norbert Seliger</u> (Technische Hochschule Rosenheim, Germany); Nico Leirich (Technical University of Applied Sciences Rosenheim, Germany)

We propose a printed circuit board (PCB) interconnection utilizing elastically deformed ribbon wires. The wire deflection is designed as a bistable snapping mechanism, which enables post-assembly tuning of the geometry. Hence, a reconfigurable inductance is obtained, easing impedance matching and supporting signal integrity. Analytical solutions for partial and mutual inductance of buckled wires are developed, which are successfully validated by magnetoquasistatic field simulations and by experiments on a test structure for frequencies ranging from 100kHz to 100MHz. We demonstrate a tunable loop inductance from 25nH to 50nH at 10MHz.

#### Paper ID: #23

#### 15:20-15:40

SPICE Based SI-PI Co-Simulation Framework to Optimize Die-Package-PCB to Meet LPDDR5(x) Performance in Automotive and Edge MPU-MCU

# Author(s): Pawan Kumar Gupta (NXP Semiconductors India, India); <u>Rohit Halba</u> (NXP Semiconductors & NXP Semiconductors India PVT. LTD., India)